Herman Casier

Michiel Steyaert

Arthur H.M. van Roermund *Editors*

# Analog Circuit Design

Robust Design, Sigma Delta Converters, RFID

## Analog Circuit Design

Herman Casier • Michiel Steyaert Arthur H. M. van Roermund Editors

## Analog Circuit Design

Robust Design, Sigma Delta Converters, RFID

Editors

Dr. Herman Casier

Consultant

Avondster 6

8520 Kuurne

Belgium

herman casier@ieee.org

Michiel Steyaert

Dept. Elektrotechniek

ESAT-MICAS

K.U. Leuven

Kardinaal Mercierlaan 94

B-3001 HEVERLEE

Belgium

michiel.steyaert@esat.kuleuven.ac.be

Prof. Arthur H. M. van Roermund Technical University Eindhoven Electrical Engineering Mixed-signal Microelectronics Group Den Dolech 2 5600 MB Eindhoven Netherlands a.h.m.v.roermund@tue.nl

ISBN 978-94-007-0390-2 e-ISBN 978-94-007-0391-9 DOI 10.1007/978-94-007-0391-9 Springer Dordrecht Heidelberg London New York

#### © Springer Science+Business Media B.V. 2011

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar S.L.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### **Preface**

This book is part of the *Analog Circuit Design* series and contains the revised contributions of all speakers of the 19<sup>th</sup> workshop on Advances in Analog Circuit Design (AACD), which was organized by Wolfgang Pribyl of Graz University of Technology. The workshop was held in the magnificent aula of the Graz University of Technology, Graz, Austria on March 23–25, 2010.

The book comprises 18 tutorial papers, divided in three chapters, each discussing a very relevant to-date topic in the area of analog circuit design. Each tutorial is presented by an expert in the field and state-of-the-art information is shared and discussed with the audience.

The topics of 2010 are:

- 1. Robust Design

- 2. Sigma Delta Converters

- 3. RFID

The aim of the AACD workshop is to bring together a group of expert designers to study and discuss new possibilities and future developments in the area of analog circuit design. Each AACD workshop has given rise to the publication of a book by Springer in their successful series of Analog Circuit Design. The series provides a valuable overview of analog circuit design and related CAD, mainly in the fields of basic analog modules, mixed-signal electronics, AD and DA converters, RF systems, robust and automotive electronics. It is a reference for whoever is engaged in these disciplines and wishes to keep abreast of the latest developments in the field. The full list of the previous books and topics in the series is enclosed below.

We sincerely hope that this 19<sup>th</sup> book continues the tradition and provides a valuable contribution to our Analog Design Community.

Herman Casier

vi Preface

**Table** Topics covered before in this series

| Table | Logics covered before in the            |                                                          |

|-------|-----------------------------------------|----------------------------------------------------------|

| 2009  | Lund (Sweden)                           | Smart Data Converters                                    |

|       |                                         | Filters on Chip                                          |

| •     | 5                                       | Multimode Transmitters                                   |

| 2008  | Pavia (Italy)                           | High-speed Clock and Data Recovery                       |

|       |                                         | High-performance Amplifiers                              |

|       |                                         | Power Management                                         |

| 2007  | Oostende (Belgium)                      | Sensors, Actuators and Power Drivers for the Automotive  |

|       |                                         | and Industrial Environment                               |

|       |                                         | Integrated PA's: from Wireline to RF                     |

|       |                                         | Very High Frequency Front Ends                           |

| 2006  | Maastricht                              | High-Speed AD Converters                                 |

|       | (The Netherlands)                       | Automotive Electronics: EMC issues                       |

|       |                                         | Ultra Low Power Wireless                                 |

| 2005  | Limerick (Ireland)                      | RF Circuits: Wide Band, Front-Ends, DAC's                |

|       |                                         | Design Methodology and Verification of RF and Mixed-     |

|       |                                         | Signal Systems                                           |

|       |                                         | Low Power and Low Voltage                                |

| 2004  | Montreux (Switzerland)                  | Sensor and Actuator Interface Electronics                |

|       |                                         | Integrated High-Voltage Electronics and Power Management |

|       |                                         | Low-Power and High-Resolution ADCs                       |

| 2003  | Graz (Austria)                          | Fractional-N Synthesizers                                |

|       |                                         | Design for Robustness                                    |

|       |                                         | Line and Bus drivers                                     |

| 2002  | Spa (Belgium)                           | Structured Mixed-Mode Design                             |

|       |                                         | Multi-Bit Sigma-Delta Converters                         |

|       |                                         | Short-Range RF Circuits                                  |

| 2001  | Noordwijk                               | Scalable Analog Circuit Design                           |

|       | (The Netherlands)                       | High-Speed D/A Converters                                |

|       | ,                                       | RF Power Amplifiers                                      |

| 2000  | Munich (Germany)                        | High-Speed A/D Converters                                |

|       | 37                                      | Mixed-Signal Design                                      |

|       |                                         | PLLs and Synthesizers                                    |

| 1999  | Nice (France)                           | (X)DSL and other Communication Systems                   |

|       | ,                                       | RF-MOST Models and Behavioural Modeling                  |

|       |                                         | Integrated Filters and Oscillators                       |

| 1998  | Copenhagen (Denmark)                    | 1-Volt Electronics                                       |

|       |                                         | Mixed-Mode Systems                                       |

|       |                                         | LNAs and RF Power Amplifiers for Communications          |

| 1997  | Como (Italy)                            | RF Analog to Digital Converters                          |

|       | 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | Sensor and Actuator Interfaces                           |

|       |                                         | Low-Noise Oscillators, PLLs and Synthesizers             |

| 1996  | Lausanne (Switzerland)                  | RF CMOS Circuit Design                                   |

| 1770  | Eddsdillie (Switzerland)                | Bandpass Delta-Sigma and Other Data Converters           |

|       |                                         | Translinear Circuits                                     |

| 1995  | Villach (Austria)                       | Low-Noise, Low-Power, Low-Voltage                        |

| 1973  | villacii (Austria)                      | Mixed-Mode design with CAD tools                         |

|       |                                         | Voltage, Current and Time References                     |

| 1994  | Eindhoven                               | Low-Power Low-Voltage                                    |

| 1774  | (The Netherlands)                       | •                                                        |

|       | (The Nemerlands)                        | Integrated Filters                                       |

|       |                                         | Smart Power                                              |

Preface vii

#### Table (continued)

| 1993 | Leuven (Belgium)                  | Mixed Analogue-Digital Circuit Design<br>Sensor Interface Circuits                                      |

|------|-----------------------------------|---------------------------------------------------------------------------------------------------------|

| 1992 | Scheveningen<br>(The Netherlands) | Communication Circuits Operational Amplifiers Analog to Digital Conversion Analog Computer Aided Design |

## **Contents**

| Part I Robust Design                                                                                                                                                                                                               | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Modeling and Design for Reliability of Analog Integrated Circuits in Nanometer CMOS Technologies                                                                                                                                   | 3   |

| Modeling and Simulation of Statistical Variability in Nanometer CMOS Technologies  A. Asenov and B. Cheng                                                                                                                          | 17  |

| Advanced Physical Design in Nanoscale Analog CMOSLanny L. Lewyn                                                                                                                                                                    | 35  |

| Robust Design for High Temperature and High Voltage Applications  Ovidiu Vermesan, Edgard Laes, Marco Ottella, Mamun Jamal, Jan Kubik,  Kafil M. Razeeb, Reiner John, Harald Gall, Massimo Abrate,  Nicolas Cordero and Jan Vcelak | 53  |

| Radiation Effects and Hardening by Design in CMOS Technologies Federico Faccio                                                                                                                                                     | 69  |

| EMC Robust Design for Smart Power High Side Switches                                                                                                                                                                               | 89  |

| Part II Sigma Delta Converters                                                                                                                                                                                                     | 105 |

| Noise-Coupled Delta-Sigma ADCS                                                                                                                                                                                                     | 107 |

| Very Low OSR Sigma-Delta Converters                                                                                                                                                                                                | 135 |

x Contents

| Comparator-Based Switched-Capacitor Delta-Sigma A/D Converters  Koen Cornelissens and Michiel Steyaert                                                                                                                                                                      | 157 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| VCO-Based Wideband Continuous-Time Sigma-Delta Analog-to-Digital Converters                                                                                                                                                                                                 | 177 |

| Wideband Continuous-Time Multi-Bit Delta-Sigma ADCs                                                                                                                                                                                                                         | 203 |

| Oversampled DACs  Andrea Baschirotto, Vittorio Colonna and Gabriele Gandolfi                                                                                                                                                                                                | 227 |

| Part III RFID                                                                                                                                                                                                                                                               | 257 |

| RFID, a Technology Ready for Industry Deployment                                                                                                                                                                                                                            | 259 |

| The World's Smallest RFID Chip Technology                                                                                                                                                                                                                                   | 277 |

| RF and Low Power Analog Design for RFID                                                                                                                                                                                                                                     | 289 |

| A Dual Frequency Band Comprehensive RFID TAG  Albert Missoni, Günter Hofer and Wolfgang Pribyl                                                                                                                                                                              | 313 |

| Printed Electronics—First Circuits, Products, and Roadmap                                                                                                                                                                                                                   | 333 |

| Towards EPC-Compatible Organic RFID Tags  Kris Myny, Soeren Steudel, Peter Vicca, Steve Smout,  Monique J. Beenhakkers, Nick A. J. M. van Aerle,  François Furthner, Bas van der Putten, Ashutosh K. Tripathi,  Gerwin H. Gelinck, Jan Genoe, Wim Dehaene and Paul Heremans | 347 |

#### **Contributors**

**Massimo Abrate** Centro Ricerche FIAT S.C.p.A., Strada Torino 50, 10043 Orbassano, Torino, Italy

**Nick A. J. M. van Aerle** Polymer Vision, Eindhoven, The Netherlands ASML, Veldhoven, The Netherlands

**A. Asenov** Department of Electronics and Electrical Engineering, The University of Glasgow, Glasgow G12 0LT, UK

Raymond Barnett Texas Instruments, Texas, USA

Henri Barthel GS1 Global Office, Brussels, Belgium

Andrea Baschirotto Department of Physics "G. Occhialini", University of Milano Bicocca, Milano, Italy e-mail: andrea.baschirotto@unimib.it

**Monique J. Beenhakkers** Polymer Vision, Eindhoven, The Netherlands

Trevor C. Caldwell Analog Devices, University of Toronto, Toronto, Canada

**B.** Cheng Department of Electronics and Electrical Engineering, The University of Glasgow, Glasgow G12 0LT, UK

**Wolfgang Clemens** PolyIC GmbH & Co.KG, Tucherstraße 2, 90763 Fürth, Germany

**Vittorio Colonna** Marvell, Pavia, Italy e-mail: vcolonna@marvell.com

**Nicolas Cordero** Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland

**Koen Cornelissens** ESAT-MICAS, K.U. Leuven, Kasteelpark Arenberg 10, 3001 Leuven, Belgium

xii Contributors

**Paolo Del Croce** Infineon Technologies AG, Siemensstrasse 2, 9500 Villach, Austria

e-mail: paolo.delcroce@infineon.com

Wim Dehaene IMEC, Leuven, Belgium;

Katholieke Universiteit Leuven, Leuven, Belgium

**Bernd Deutschmann** Infineon Technologies AG, Am Campeon 1–12, 85579 Neubiberg, Germany

e-mail: bernd.deutschmann@infineon.com

**V. Dhanasekaran** Electrical and Computer Engineering, Analog and Mixed-Signal Center, Texas A&M University, College Station, TX, USA

Federico Faccio PH dept., CERN, 1211 Geneva 23, Switzerland

François Furthner TNO Science and Industry, Eindhoven, The Netherlands

**Harald Gall** austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria

**M. Gambhir** Electrical and Computer Engineering, Analog and Mixed-Signal Center, Texas A&M University, College Station, TX, USA

Gabriele Gandolfi Marvell, Pavia, Italy

e-mail: gabriele@marvell.com

Gerwin H. Gelinck TNO Science and Industry, Eindhoven, The Netherlands

Jan Genoe IMEC, Leuven, Belgium;

Katholieke Hogeschool Limburg, Diepenbeek, Belgium

**Georges Gielen** ESAT-MICAS, Katholieke Universiteit Leuven, Leuven, Belgium

e-mail: gielen@esat.kuleuven.be

Paul Heremans IMEC, Leuven, Belgium

Katholieke Universiteit Leuven, Leuven, Belgium

Günter Hofer Infineon Technologies Austria AG, Graz, Austria

**Mamun Jamal** Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland

**Reiner John** Infineon Technologies AG, Am Campeon 1-12, 85579 Neubiberg, Germany

**Jürgen Krumm** PolyIC GmbH & Co.KG, Tucherstraße 2, 90763 Fürth, Germany

Jan Kubik Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland

**Edgard Laes** ON Semiconductor Belgium BVBA, Senneberg, J. Monnetlaan, 1804 Vilvoorde, Belgium

Contributors xiii

Kyehyung Lee Conexant Systems, Newport Beach, CA 92660, USA

**Lanny L. Lewyn** Lewyn Consulting Inc., Laguna Beach, CA, USA e-mail: lanny@pacbell.net

**C.-Y. Lu** Electrical and Computer Engineering, Analog and Mixed-Signal Center, Texas A&M University, College Station, TX, USA

Elie Maricau ESAT-MICAS, Katholieke Universiteit Leuven, Leuven, Belgium

**Albert Missoni** Infineon Technologies Austria AG, Graz, Austria; Graz University of Technology Institute of Electronics, Graz, Austria

**Kris Myny** IMEC, Leuven, Belgium; Katholieke Hogeschool Limburg, Diepenbeek, Belgium; Katholieke Universiteit Leuven, Leuven, Belgium

**Marco Ottella** Centro Ricerche FIAT S.C.p.A., Strada Torino 50, 10043 Orbassano, Torino, Italy

**M. Onabajo** Electrical and Computer Engineering, Analog and Mixed-Signal Center, Texas A&M University, College Station, TX, USA

**Michael H. Perrott** SiTime Corporation, Sunnyvale, USA e-mail: mhperrott@gmail.com

**Wolfgang Pribyl** Graz University of Technology Institute of Electronics, Graz, Austria

Bas van der Putten TNO Science and Industry, Eindhoven, The Netherlands

**J. Silva-Martinez** Electrical and Computer Engineering, Analog and Mixed-Signal Center, Texas A&M University, College Station, TX, USA

Kafil M. Razeeb Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland

**F. Silva-Rivas** Electrical and Computer Engineering, Analog and Mixed-Signal Center, Texas A&M University, College Station, TX, USA

Steve Smout IMEC, Leuven, Belgium

Soeren Steudel IMEC, Leuven, Belgium

Michiel Steyaert Dept. Elektrotechniek, ESAT-MICAS, K.U. Leuven, Kardinaal Mercierlaan 94, B-3001 Heverlee, Belgium e-mail: michiel.steyaert@esat.kuleuven.ac.be

Gabor C. Temes Oregon State University, Corvallis, OR 97331, USA

Ashutosh K. Tripathi TNO Science and Industry, Eindhoven, The Netherlands

Mitsuo Usami Central Research Laboratory, Hitachi Ltd., 1-280 Higashi-Koigakubo, Kokubunji-shi, 185-8601 Tokyo, Japan e-mail: mitsuo.usami.fc@hitachi.com

xiv Contributors

**Jan Vcelak** Tyndall National Institute, Lee Maltings, Prospect Row, Cork, Ireland

**Ovidiu Vermesan** SINTEF, Forskningsvn. 1, P.O.Box 124 Blindern, 0314 Oslo, Norway

Peter Vicca IMEC, Leuven, Belgium

Pieter De Wit ESAT-MICAS, Katholieke Universiteit Leuven, Leuven, Belgium

## Part I Robust Design

In this first day of the AACD workshop in Graz, the state-of-the-art of robust design is discussed. The same topic also figured in the AACD program of 2003, also in Graz. The program then focussed on ESD in analog, smart power and RF applications, on EMC in automotive applications and on substrate coupling. The program of this year presents in-depth discussions of robust design in nanometer technologies, in high-temperature and high-voltage environments, in the presence of radiation and of conductive EMC.

The first three contributions deal with different aspects of robust design in nanometer technologies. The first addresses analysis tools and design solutions for the variability and reliability problems in analog circuits in nanometer CMOS technologies. A tool is presented to evaluate the impact of degradation on circuit performance and to identify reliability weak spots. It is also shown how digitally assisted analog design can be used to improve the resilience for variability and degradation of analog circuits.

The second contribution focuses on statistical variability in nanometer CMOS. Discreteness of charge and matter, atomic scale non-uniformities and material granularity are discussed and their expected impact on transistor parameters and on the variability sensitive SRAM cell in sub-45nm technologies is described. It is shown that a seven parameter statistical BSIM model accurately matches the physically simulated device characteristics.

The third paper identifies physical factors, which adversely affect sub-100nm CMOS analog designs and proposes methods for mitigating or overcoming them. It is shown that these methods require design restrictions at the circuit design stage as well as layout restrictions at the physical design stage. The historical separation between circuit and physical design activities must be replaced by a more close cooperation between them.

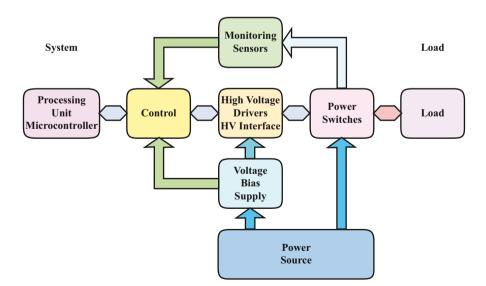

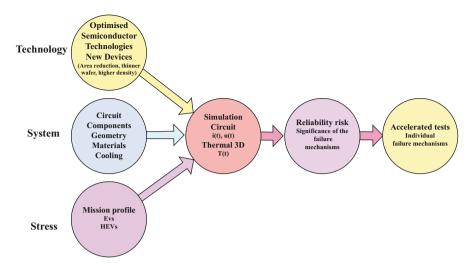

The next three papers deal with robust design for different hostile environments. The first of these contributions addresses high-temperature and high-voltage integrated electronics and modules for electric power systems in electric and hybrid-electric vehicles. Maximization of the compatibility between semiconductor, packaging and material technologies, thermal-electric simulation and reliability calculation of the whole configuration are key elements for robust smart power modules.

2 H. Casier

The next work is about radiation effects and hardening-by-design techniques in modern deep-submicron CMOS technologies. Both cumulative and single-event effects are discussed. Hardening-by-design techniques, leveraging on the intrinsic radiation tolerance of CMOS, are detailed for both effects. These techniques allow for the design of robust circuits with high radiation tolerance in a commercial-grade state-of-the-art CMOS technology instead of a dedicated radiation-hard technology.

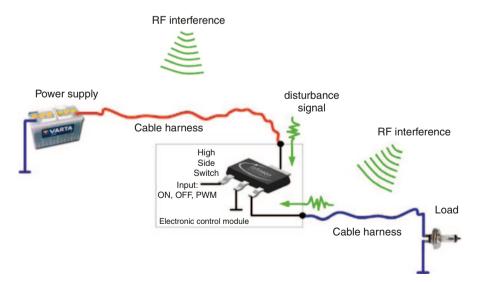

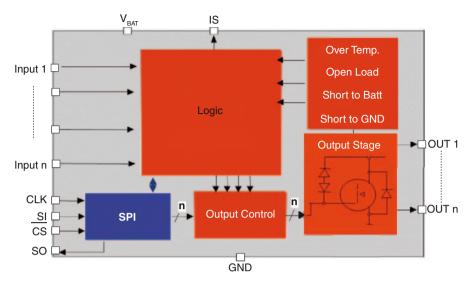

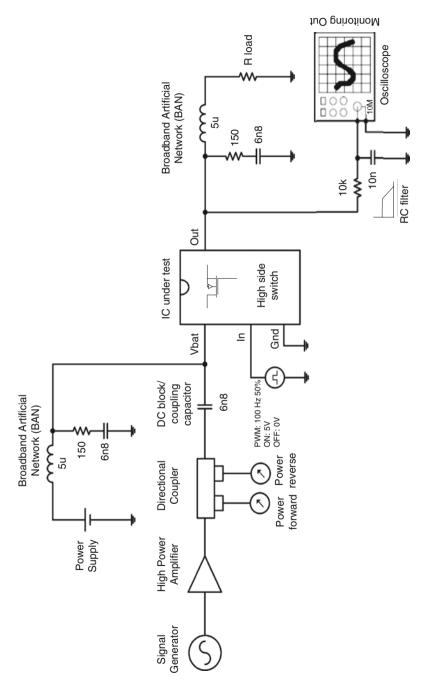

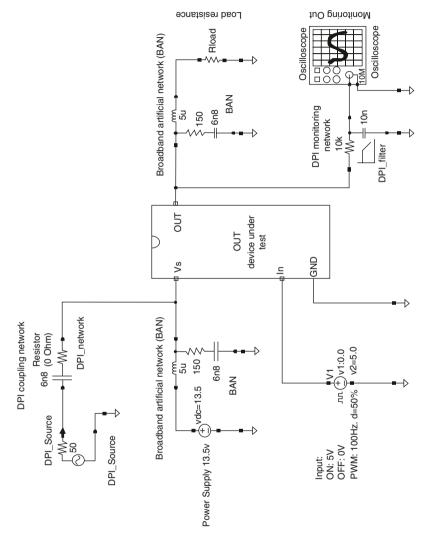

The last contribution first shows how the standardized direct power injection measurement test bench can be transferred to the simulation environment to predict the EMC immunity of a smart power circuit. This simulation environment is then used to optimize a new methodology for robust high-side smart power switches, based on pin impedance control. Measurements endorse the validity and accuracy of this approach.

Herman Casier

## Modeling and Design for Reliability of Analog Integrated Circuits in Nanometer CMOS Technologies

Georges Gielen, Elie Maricau and Pieter De Wit

#### 1 Introduction

The evolution towards nanometer CMOS technologies (90, 65, 45 nm and below) [1] has enabled the design of complex Systems on a Chip (SoC) in consumer-market applications such as telecom and multimedia. These integrated systems are increasingly mixed-signal designs, embedding high-performance analog or mixed-signal blocks and possibly sensitive RF frontends together with complex digital circuitry (multiple processors, some logic blocks, and several large memory blocks) on the same chip. Even when developing a heterogeneous System in Package (SiP), the digital dies will likely have several embedded analog blocks.

The use of CMOS nanometer technologies however also brings significant challenges for the actual circuit design (both analog and digital) that were not encountered before. These challenges include [2]:

- managing the ever increasing design complexities in tightening time-to-market constraints, which requires proper EDA methodologies and tools to increase designer efficiency (e.g. using analog synthesis tools), as well as to verify full mixed-signal systems;

- the increasing variability of technology parameters, causing mismatch and yield problems;

- aggravating degradation mechanisms (e.g. NBTI, Hot Carriers) and increasing reliability constraints such as EMC/EMI regulations.

This chapter addresses analysis tools and design solutions for the variability and reliability problems in analog circuits. After describing the degradation phenomena, it presents tools for the efficient analysis and identification of reliability problems in analog circuits. In addition, it describes circuit techniques for run-time reconfiguration of the analog circuits to make them degradation-resilient. The chapter is organized as follows. Section 2 briefly describes the problems of variability- and

G. Gielen (⊠)

ESAT-MICAS, Katholieke Universiteit Leuven, Leuven, Belgium e-mail: gielen@esat.kuleuven.be

reliability-induced circuit performance degradation. Section 3 outlines an approach for the reliability analysis and the detection of reliability weak spots in analog circuits. An efficient extension to include the effect of variability is included as well. Section 4 then presents run-time circuit self-adaptation techniques to make them degradation-resilient. This concept is illustrated with a practical design example. Finally, Sect. 5 provides conclusions.

#### 2 Variability- and Reliability-Induced Analog Circuit Performance Degradation

Many non-idealities in analog circuits originate from random and systematic errors in the implementation of the circuit. These errors represent the time-independent reliability problems in a circuit. Although the random errors are unknown at the time of design, they can largely be compensated or calibrated away after fabrication. Time-dependent degradation on the other hand occurs due to ageing of the transistors over time, which results in the circuit performance changing over time, hence possibly turning initially fully functional circuits into nonfunctional circuits. Also disturbance sources such as electromagnetic interference (EMI) or substrate noise coupling may turn functional analog circuits into nonfunctional circuits, but normally don't change performance permanently, so we will not focus on these in this chapter. We will now describe the variability and degradation effects in some more detail.

#### 2.1 Variability and Mismatch

Random errors, usually denoted as variability, are the result of the stochastic nature of many physical processes that take place during the fabrication of integrated circuits, such as line edge roughness and random dopant fluctuations. In analog circuits device mismatch between identically designed devices is a key limitation to the accuracy of the circuit. For example, to first order the threshold voltage mismatch  $\Delta V_T$  between identical transistors with active area WL is given by [3, 4]:

$$\sigma^{2}(\Delta V_{T}) = \frac{A_{VT}^{2}}{WL} + S_{VT}^{2}D^{2}$$

(1)

where  $A_{VT}$  and  $S_{VT}$  are process-dependent constants and D is the distance between the devices. Unfortunately, as can be seen from (1), this mismatch is inversely proportional to the area of the devices and therefore can only be improved by making the devices larger. This implies more chip area and more power for the same speed.

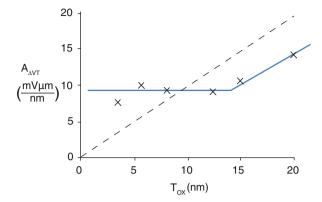

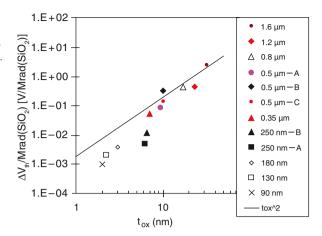

Fig. 1 Evolution of the threshold voltage mismatch parameter as a function of the gate oxide thickness according to [5]. ( $A_{\Delta VT}$  is the parameter characterizing threshold voltage mismatch in (1) [3, 4])

In addition, as shown in Fig. 1, Tuinhout observed that, although historically this mismatch was improving with scaling technology, for values of gate oxide thickness below 10 nm, this improvement seems to level off, indicating that mismatch is no longer improving much with technology progress. This might significantly reduce the benefits of technology scaling for analog integrated circuits [5].

#### 2.2 Time-Dependent Degradation

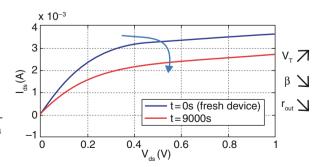

Time-dependent degradation effects cause a change of the transistor parameters  $(V_T, \beta, r_o)$  as a function of time and therefore might turn an initially fully functional circuit into a less or even non-functional circuit over time [6]. This degradation depends on the stress applied to the device, i.e. the voltages and currents applied to the transistor, as well as the transistor sizes and the temperature. Figure 2 qualitatively indicates the impact of these mechanisms on the  $I_{DS}$ – $V_{DS}$  characteristic of a MOS device for an arbitrary stress time. Some of the most important degradation mechanisms will now be discussed in more detail.

Fig. 2 Time-dependent variation of the characteristics of a transistor due to Hot-Carrier and NBTI degradation [6]

#### 2.2.1 Time-Dependent Dielectric Breakdown

In ultra-scaled MOSFETs, the strong electric fields across the gate oxide can cause oxide damage leading to dielectric breakdown (BD), i.e. the loss of the isolating properties of the oxide. BD is an extremely local phenomenon, for which an extra current flows through a small region of the gate oxide. Prior to oxide BD, a degradation process of the dielectric takes place that initiates the generation of traps in random positions inside the oxide and at the interface. A stress-induced leakage current is produced during this degradation stage. If the dielectric degradation increases, a critical trap density is reached and BD occurs [7, 8]. Due to this behavior the time to BD can be described using a Weibull probability distribution. Obviously this breakdown phenomenon influences the circuit performance over time, eventually resulting in circuit failure.

#### 2.2.2 Hot-Carrier Injection

A second degradation phenomenon is Hot Carrier Injection (HCI), which manifests itself mainly as a threshold voltage shift, and some degradation of carrier mobility and a change of output resistance [9, 10]. During hot carrier stress, which consists of a large electric field near the drain end of a transistor in saturation, hot carriers are produced. These carriers introduce both oxide and interface traps (near the drain) and a substrate current. As holes are much 'cooler' than electrons, hot carrier effects in nMOS devices are proven to be more significant than in pMOS devices [11]. Removal of the stress anneals some of the interface traps, resulting in partial recovery. But as these traps are only present at the drain junction of the transistor, this recovery is negligible in comparison to NBTI relaxation (see next subsection).

HCI degradation is typically modeled with a power law dependence on the stress time t [10]. For example, the increase in threshold voltage  $V_T$  over time can be written as:

$$\Delta V_T = A(V_{GS}, V_{DS}, T, W, L \dots) t^n$$

(2)

where the function A depends on the applied voltages, the temperature T but also on the transistor width W and length L. In the case of HCI, the exponent n is in the order of 0.45. A full model can be found in [12]. Due to hot carrier degradation, transistors degrade over time, which translates to a change in the circuit performance over time. Therefore, tools need to be developed to analyze this problem and to identify possible reliability problems in a circuit before tapeout. This will be described in Sect. 3. Circuit techniques to deal with this kind of degradation also need to be developed and will be described in Sect. 4.

#### 2.2.3 Negative Bias Temperature Instability

Negative Bias Temperature Instability (NBTI) has an increasingly adverse impact on nanometer CMOS technology [13]. NBTI is typically seen as a threshold voltage

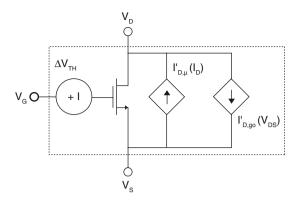

Fig. 3 Equivalent model of transistor to model degradation due to Hot Carriers or NBTI

shift after a negative bias has been applied to a MOS gate at elevated temperature, hence mainly affecting pMOS transistors [14]. Degradation of channel carrier mobility is also observed. The NBTI degradation is typically represented as following a power law with stress time t similar to Eq. 2, but with the exponent n typically being around 0.18 and with a different function A. The reciprocal PBTI behavior in nMOS transistors is still less important.

A peculiar property of the NBTI mechanism is the so-called relaxation or recovery of the degradation immediately after the stress voltage has been reduced [15]. This relaxation behavior greatly complicates the evaluation of NBTI, its modeling and the extrapolation of its impact on circuitry. A complete model of NBTI for circuit analysis has however not yet been fully established.

Since HCI and NBTI impact both the transistor parameters  $V_T$ ,  $\beta$ , and  $r_o$ , this can be modeled by replacing the transistor in the circuit netlist by a subcircuit as shown in Fig. 3. The additional sources model the change in  $V_T$ ,  $\beta$ , and  $r_o$  according to Eq. 2, so that the intrinsic device model, e.g. BSIM, can be used for the actual transistor. This allows to simulate a degraded circuit with a standard SPICE simulator, with an additional script to update the values of the extra sources according to Eq. 2.

#### 3 Reliability Analysis of Analog Integrated Circuits

Due to the impact of degradation on integrated circuits, it is important to analyze quantitatively the impact of HCI and NBTI on the performance and lifetime of a circuit, and to identify potential reliability problems in a circuit at design time, so that—if needed—the design can be modified to guarantee correct functionality and performance over the lifetime of the electronic product. Therefore, proper reliability simulation and analysis tools are needed for analog circuits.

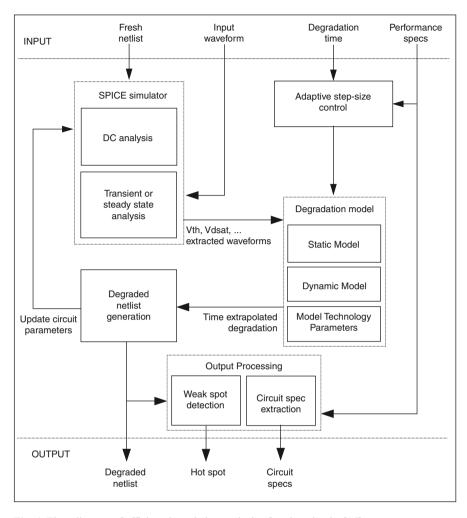

In [16] an efficient method for reliability simulation of electronic circuit is presented. It uses a short transient simulation that provides accurate information about the stress at every circuit node, while a degradation extrapolation ensures a fast simulation result. Figure 4 gives a schematic representation of this reliability simulation algorithm. The input to the simulator is a fresh (i.e. unstressed) netlist. A transient simulation over time  $T_{tr}$  with step size  $t_{tr}$  is performed on the input netlist. As circuit

Fig. 4 Flow diagram of efficient degradation analysis of analog circuits [16]

input a periodic time-varying signal,  $v_{in}(t)$ , with period  $T_{in}$  is applied. The impact of completely arbitrary (i.e. non-periodic) input signals can only be calculated using a transient analysis over the entire operating period of the circuit, which obviously is not very feasible. Since the operation of most electronic systems is based on the execution of periodically executed algorithms (e.g. MPEG encoding), the restriction to periodic input signals is not a real limitation. Once the stress pattern on every transistor node is calculated from this initial simulation, it is extracted and passed on to a degradation model based on Eq. 2, which extrapolates the transistor degradation to the desired circuit operation time. Finally, a degraded version of the netlist is created as an output, using equivalent models like Fig. 3 for the individual transistors. A designer can use this output netlist to study the impact of degradation on the circuit performances and to identify the reliability weak spots.

In [17] the simulation method has also been extended to take variability of the device parameters into account. The initial approach of using Monte-Carlo simulations was replaced by design of experiments (DOE) techniques, resulting in a speed improvement of up to 4 orders of magnitude compared to standard Monte-Carlo, while maintaining the same simulation accuracy. In order to obtain a quasi-linear computational complexity, first a screening is performed to eliminate unimportant parameters, followed by a set of regression designs to build a response surface model used for the actual statistical analysis.

#### 3.1 Illustrative Circuit Example

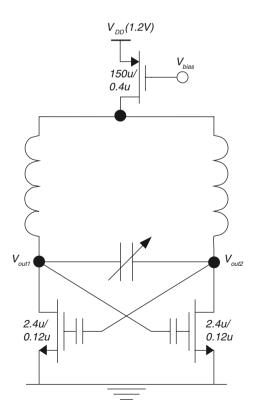

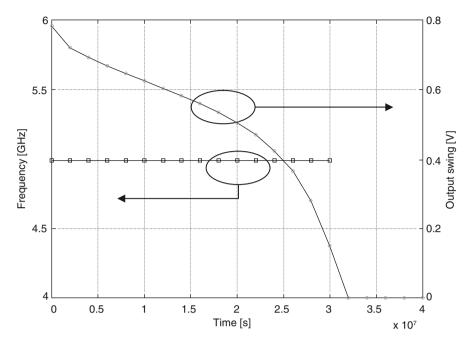

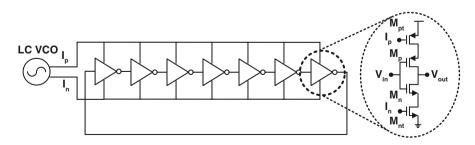

To illustrate the variability-aware reliability simulation methodology, the LC-VCO of Fig. 5 is analyzed [17]. Both HC and NBTI degradation are included. The example is simulated in a 90 nm CMOS technology. Large voltages at the drains of the cross-coupled transistor pair cause these transistors to suffer from hot-carrier degradation. Figure 6 shows the effect of degradation on both the oscillation frequency and the output swing for nominal design parameters (no statistical variations). The

**Fig. 5** Circuit schematic of the LC-VCO

Fig. 6 Frequency and output swing of the LC-VCO as a function of time due to hot carrier degradation

frequency of the LC-oscillator is not affected by degradation; the output swing, however, decreases significantly over time. For the (slightly overstressed) settings used, the circuit fails after six months, if we assume that the device is considered to be defective when Vout < 0.6 V.

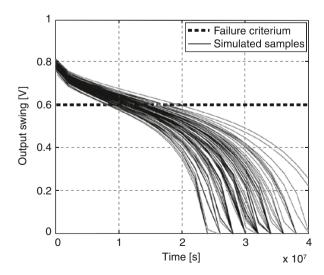

**Fig. 7** Variability-induced dispersion of the time to failure of the LC-VCO

Now let us consider process variability. Figure 7 shows the failure time dispersion of the oscillator due to local and global errors of transistor parameters. Clearly, there is a large spread. Although a reliability simulation of the nominal circuit (not including variability) indicates a failure time of six months (see Fig. 6), running a variability-aware reliability simulation shows that 20% of the circuits already fail in less than four months.

## 4 Circuit Techniques for Variability and Degradation Resilience

The mechanisms described in Sect. 2 may cause serious performance changes and hence reliability problems in nanometer CMOS electronic systems. The classical approaches, i.e. guaranteeing intrinsic robustness by worst-case overdesign or use of redundancy, introduce an unacceptable power and area penalty. In order to obtain a high-performance and reliable system, using nanometer technologies, novel circuit design techniques are needed to deal with variability and time-dependent degradation. Some of these will be discussed here briefly.

#### 4.1 Solutions to Processing Variability

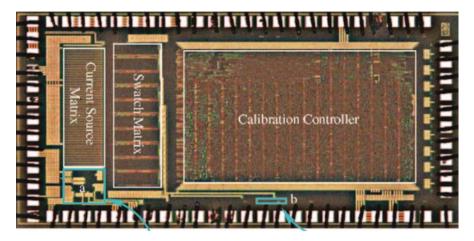

Although mismatch is statistical in the sense that it is unknown before fabrication, it is fixed after fabrication. Therefore, all such static time-independent errors can to large extent be compensated for after fabrication using post-fabrication calibration methods. An example of this calibration technique has been proposed and verified on silicon in [18] where it is applied on the design of a 14-bit 200 MHz current-steering DAC. The high accuracy is obtained using a Switching-Sequence Post-Adjustment (SSPA) calibration technique, which dynamically rearranges the switching sequence of the unary MSB current sources. Since this technique is applied after chip fabrication (i.e. calibration at run time), random errors can partially be cancelled out. As a result, the area requirement imposed by the *INL* property (INL < 0.5LSB), which intrinsically would require a large area to sufficiently reduce the mismatch, is reduced dramatically to only 6% of the area of an intrinsicaccuracy DAC [19]. The only extra analog building block needed is an accurate current comparator. A chip photograph is shown in Fig. 8. The total area of the chip is 3 mm<sup>2</sup>, where the area of the analog part is only 0.28 mm<sup>2</sup>. The area of the digital part (mainly the calibration controller) is still quite large in this version, but will be scaled significantly in advanced processes.

This type of heavy-digital analog circuit design corresponds to the paradigm of digitally assisted analog circuits [20], where the analog part is actually under-sized to meet the required performances intrinsically, but where digital circuitry corrects for the errors or the nonidealities through reconfiguration or calibration.

Fig. 8 Chip microphotograph of current-steering DAC with post-fabrication calibration [18]

#### 4.2 Solutions to Time-Dependent Degradation

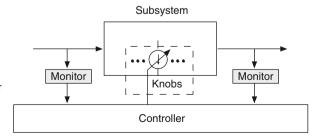

The solution to the time-dependent problem can be found in the use of monitors and knobs as presented in [21, 22]. The idea is to continuously monitor the operation of a system or circuit and take runtime countermeasures to compensate for variability and reliability errors. This guarantees a correct and optimal operation at all times, if properly anticipated at design time by using analysis and design tools such as presented in Sect. 3. As shown in Fig. 9, such a system consists of three parts. *Monitors* measure the actual performance of the system. Simple measurement circuits are required to achieve this. *Knobs* are tunable or reconfigurable circuit parts able to change the operating settings of the system. Finally, a *Control Algorithm* selects, based on the inputs from the different monitors, the optimal configuration of the system knobs in order to satisfy the system specifications, even if the performance varies over time. The control loop can be implemented in digital hardware, adding only a limited amount of extra power dissipation and area consumption. Note that this concept can be applied to both analog and digital circuits.

Fig. 9 Principle schematic of knobs and monitors concept to overcome degradation and failures

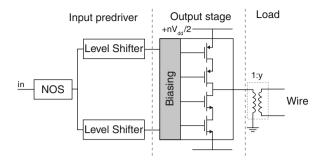

**Fig. 10** Schematic of high-voltage line driver

The advantages of a system with knobs and monitors are:

- a self-adaptive system is obtained. It compensates for variability and degradation-induced errors as they occur, thus keeping the system in its optimal operation point of specifications and operating conditions.

- overdesign is not needed anymore. Design specifications for a given circuit can

be relaxed because multiple possible operating modes exist within one system.

This results in an overall decrease in power dissipation and area consumption of

the entire system. Switching to another operating point might cause a slightly

larger power consumption, but correct operation is guaranteed at any time, which

is a reasonable trade-off in safety-critical applications that demand absolute reliability.

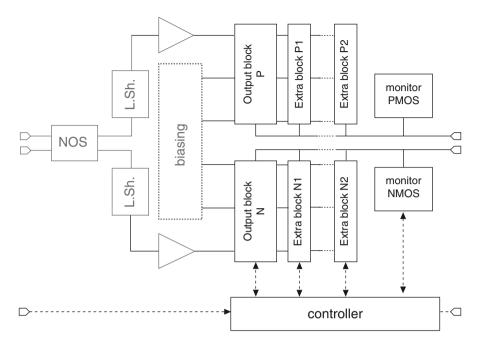

As an example, Fig. 10 shows a high-voltage line driver circuit. Due to the high voltages used, the output transistors degrade over time in nanometer CMOS technologies. Since the power efficiency of the line driver is directly linked to the on-resistance of the output transistors which degrades over time, solutions to guarantee the reliable operation with high power efficiency have to be found. As shown in Fig. 11, this can be solved by making the circuit reconfigurable [23]. Extra sub-transistor blocks  $P_i$  and  $N_i$  are added, besides the monitor circuits and the controller. The resilience of the circuit is defined as the minimum efficiency loss the system can detect and correct. If the circuit exceeds this limit, i.e. if the efficiency drops below the minimum set value, then the circuit needs to reconfigure and heal itself to "crank up" the efficiency again. To this end, extra sub-transistors (the extra "blocks" in Fig. 11) are added to the output transistors. These sub-transistors can be switched on under digital control. Monitor circuits are added to the line driver to monitor the actual degradation of the output transistors. They feed their information to the controller that decides on turning on extra sub-transistors.

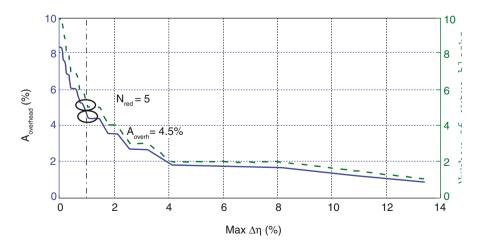

Obviously, all this requires extra chip area. The system-level trade-off between the granularity of the extra sub-transistors, the circuit resilience and the extra area overhead has been elaborated in [23]. Figure 12 shows the area overhead as a function of the ripple on the power efficiency  $\Delta \eta$ . Clearly, for a degradation of

Fig. 11 Modified output stage of the high-voltage line driver with extra parallel sub-transistors to make the circuit failure-resilient [23]

the power efficiency with maximum a couple percent, the circuit can be made degradation-resilient with an area overhead of 4–5%, which is quite acceptable compared to worst-case overdesign of the circuit. Also the power consumption is improved.

Fig. 12 Trade-off between area overhead and granularity of the extra subtransistors, which is directly related to the allowed "ripple"  $\Delta \eta$  on the power efficiency [23]

#### 5 Conclusions

CMOS technology is evolving deeper and deeper into the nanometer era, enabling the integration of entire systems, many of which are mixed-signal in nature. This paper has described solutions to variability and reliability challenges posed by these nanometer CMOS technologies. The problem of time-dependent performance degradation due to breakdown, hot carriers or NBTI has been described and models have been proposed. Next, an efficient tool for the analysis and identification of reliability problems in analog circuits has been described. The tool allows identifying potential ageing problems in circuits. An efficient approach to analyze the effect of variability on the reliability has been developed too. Finally, run-time circuit adaptation/reconfiguration techniques have been proposed to make circuits failure-resilient so that they can self-recover from degradation. These techniques are fully compliant with the trend towards digitally assisted analog circuits. All this has been illustrated with several design examples.

**Acknowledgements** The authors acknowledge the financial support of FWO, IWT SBO Elixir and EU FP7 Reality for different parts of this work.

#### References

- 1. ITRS 2008 technology roadmap. http://public.itrs.net/

- G. Gielen, W. Dehaene, Analog and digital circuit design in 65 nm CMOS: end of the road?, in *Proceedings DATE Conference*, March 2005, vol. 1, pp. 37–42

- K. Lakshmikumar et al., Characterisation and modeling of mismatch in MOS transistors for precision analog design. IEEE J. Solid-State Circ. 21(6), 1057–1066 (1986)

- M. Pelgrom et al., Matching properties of MOS transistors. IEEE J. Solid-State Circ. 24(5), 1433–1439 (1989)

- H. Tuinhout, Impact of parametric mismatch and fluctuations on performance and yield of deep-submicron CMOS technologies, in *Proceedings ESSDERC*, 2002

- G. Gielen et al., Emerging yield and reliability challenges in nanometer CMOS technologies, in *Proceedings DATE Conference*, 2008, pp. 1322–1327

- 7. J. Stathis, Physical and predictive models of ultrathin oxide reliability in CMOS devices and circuits. IEEE Trans. Dev. Mater. Reliab. 1, 43 (2001)

- 8. B. Kaczer et al., Analysis and modeling of a digital CMOS circuit operation and reliability after gate oxide breakdown: a case study. Microelectron. Reliab. 42, 555 (2002)

- I. Kurachi et al., Physical model of drain conductance, gd, degradation of NMOSFET's due to interface state generation by hot carrier injection. IEEE Trans. Electron. Dev. 41, 1618 (1994)

- W. Wang et al., Compact modeling and simulation of circuit reliability for 65 nm CMOS technology. IEEE Trans. Dev. Mater. Reliab. 7(4) 509–517 (2007)

- C. Hu et al., Hot-electron-induced MOSFET degradation—model, monitor, and improvement. IEEE Trans. Electron. Dev. ED-32, 375–384 (1985)

- E. Maricau, P. De Wit, G. Gielen, An analytical model for hot carrier degradation in nanoscale CMOS suitable for the simulation of degradation in analog IC applications. Microelectron. Reliab. 48(8–9), 1576–1580 (2008)

- 13. D. Schroder et al., Negative bias temperature instability: road to cross in deep submicron silicon semiconductor manufacturing. J. Appl. Phys. **94**, 1 (2003)

J. Stathis et al., The negative bias temperature instability in MOS devices: a review. Microelectron. Reliab. 46, 270–286 (2006)

- 15. G. Chen et al., Dynamic NBTI of PMOS transistors and its impact on device lifetime, in *Proceedings Reliability Physics Symposium*, 2003

- E. Maricau, G. Gielen, Reliability simulation of analog ICs under time-varying stress in nanoscale CMOS, in *Proceedings DRV Workshop*, 2008

- 17. E. Maricau, G. Gielen, A quasi-linear deterministic variation-aware circuit reliability simulation methodology, in *Proceedings DATE Conference*, 2010

- T. Chen, G. Gielen, A 14-bit 200-MHz current-steering DAC with switching-sequence postadjustment calibration. IEEE J. Solid-State Circ. 42, 2386–2394 (2007)

- G. Van der Plas, et al., A 14-bit intrinsic accuracy Q<sup>2</sup> random walk high-speed CMOS DAC. IEEE J. Solid-State Circ. 34(12), 1708–1718 (1999)

- 20. B. Murmann, Digitally assisted analog circuits. IEEE Micro. 26(2), 38-47 (2006)

- A. Papanikolaou, Reliability issues in deep deep submicron technologies: time-dependent variability and its impact on embedded system design. 13<sup>th</sup> IEEE International On-Line Testing Symposium (IOLTS 2007)

- B. Dierickx, Designing with unreliable components, invited presentation at the 2007 IET-FSA meeting, 14-15 May 2007, Paris

- 23. P. De Wit, G. Gielen, System-level design of a self-healing, reconfigurable output driver, in *Proceedings DRV Workshop*, 2008

# Modeling and Simulation of Statistical Variability in Nanometer CMOS Technologies

A. Asenov and B. Cheng

#### 1 Introduction

The years of 'happy scaling' are over and the fundamental challenges that the semi-conductor industry faces at technology and device level will deeply affect the design of the next generations of integrated circuits and systems. The progressive scaling of CMOS transistors to achieve faster devices and higher circuit density has fuelled the phenomenal success of the semiconductor industry—captured by Moore's famous law [1]. Silicon technology has entered the nano CMOS era with 35 nm MOSFETs in mass production in the 45 nm technology generation. However, it is widely recognised that the increasing variability in the device characteristics is among the major challenges to scaling and integration for the present and next generation of nano CMOS transistors and circuits. The statistical variability of transistor characteristics, which has been previously concern only in the analogue design domain, has become a major concern associated with CMOS transistors scaling and integration [2, 3]. It already critically affects SRAM scaling [4], and introduces leakage and timing issues in digital logic circuits [5].

In the next section we review the major sources of statistical variability in nano CMOS transistors focusing at the 45 nm technology generation and beyond. In Sect. 3 we use advanced 3D physical statistical simulation to forecasts the magnitude of statistical variability in contemporary and future CMOS devices. The compact model strategies suitable for capturing the statistical variability in industrial strength compact models such as BSIM and PSP are outlined in Sect. 4. Section 5 presents example of statistical SRAM circuit simulation employing the statistical compact model strategies discussed in Sect. 4. Finally the conclusions are drawn in Sect. 6

Department of Electronics and Electrical Engineering, The University of Glasgow, Glasgow, G12 0LT, UK

A. Asenov (⊠)

#### 2 Sources of Statistical Variability

The statistical variability in modern CMOS transistors is introduced by the inevitable discreteness of charge and matter, the atomic scale non-uniformity of the interfaces and the granularity of the materials used in the fabrication of integrated circuits.

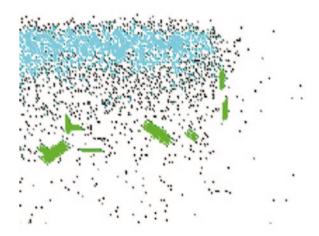

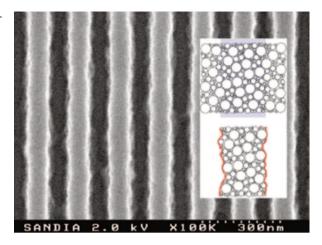

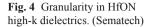

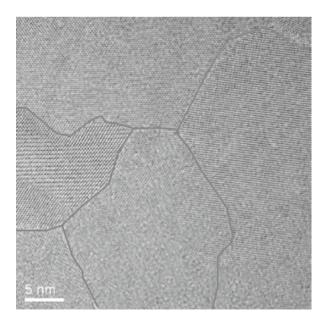

The granularity introduces significant variability when the characteristic size of the grains and irregularities become comparable to the transistor dimensions. For conventional bulk MOSFETs, which are still the workhorse of the CMOS technology, Random Discrete Dopants (RDD) are the main source of statistical variability [6]. Random dopants are introduced predominantly by ion implantation and redistributed during high temperature annealing. Figure 1 illustrates the dopant distribution obtained by the atomistic process simulator DADOS by Synopsys. Apart from special correlation in the dopant distribution imposed by the silicon crystal lattice, there may be also correlations introduced by the Coulomb interactions during the diffusion process. Line Edge Roughness (LER) illustrated in Fig. 2 stems from the molecular structure of the photoresist and the corpuscular nature of light. The polymer chemistry of the 193 nm lithography used now for few technology generations mainly determines the current LER limit of approx 5 nm [7]. In transistors with poly-silicon gate Poly Gate Granularity (PGG) illustrated in Fig. 3 is another important source of variability. This is associated surface potential pinning at the grain boundaries complimented by doping non-uniformity due to rapid diffusion along the grain boundaries [3].

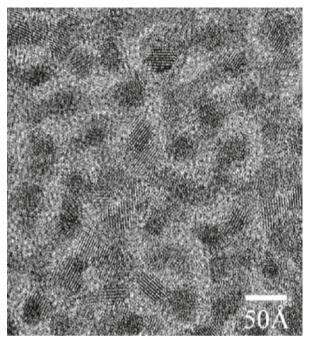

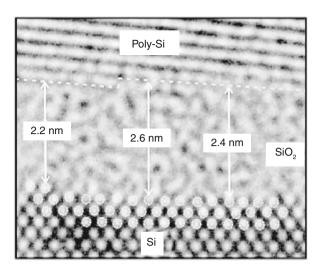

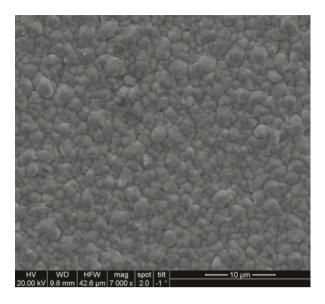

The introduction of high-k/metal gate technology improves the RDD induced variability, which is inversely proportional to the equivalent oxide thickness (EOT). This is due to the elimination of the polysilicon depletion region and better screening of the RDD induced potential fluctuations in the channel from the very high concentration of mobile carriers in the gate. The metal gate also eliminates the PGG induced variability. In the same time it introduces high-k granularity illustrated in Fig. 4 and variability due to work-function variation associated with the metal gate granularity

**Fig. 1** KMC simulation of RDD. (DADOS, Synopsys)

**Fig. 2** Typical LER in photoresist. (Sandia Labs)

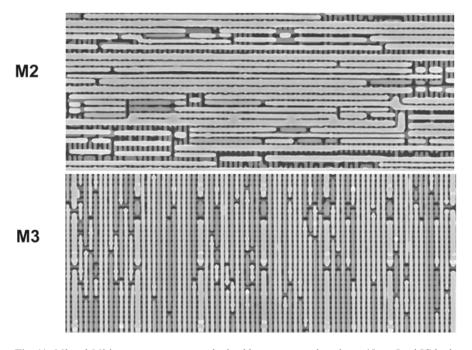

**Fig. 3** SEM micrograph of typical PSG from bottom

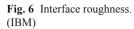

illustrated in Fig. 5 [8]. In extremely scaled transistors atomic scale channel interface roughness illustrated in Fig. 6 [9] and corresponding oxide thickness and body thickness variations [10] can become important source of statistical variability.

#### 3 Statistical Variability in Advanced CMOS Devices

The simulation results presented in this chapter were obtained using the Glasgow statistical 3D device simulator, which solves the carrier transport equations in the drift-diffusion approximation with Density Gradient (DG) quantum corrections

[11]. In the simulations, the RDD are generated from continuous doping profile by placing dopant atoms on silicon lattice sites within the device S/D and channel regions with a probability determined by the local ratio between dopant and silicon atom concentration. Since the basis of the silicon lattice is 0.543 nm a fine mesh of

Fig. 5 Metal granularity causing gate work-function variation

0.5 nm is used to ensure a high resolution of dopant atoms. However, without considering quantum mechanical confinement in the potential well, in classical simulation, such fine mesh leads to carrier trapping at the sharply resolved Coulomb potential wells generated by the ionised discrete random dopants. In order to remove this artifact, the DG approach is employed as a quantum correction technology for both electrons and holes [11].

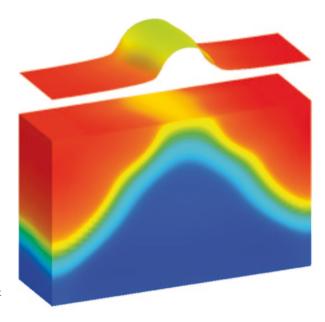

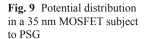

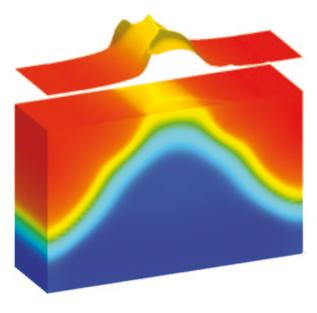

The LER illustrated in Fig. 4 is introduced through 1D Fourier synthesis. Random gate edges are generated from a power spectrum corresponding to a Gaussian autocorrelation function [9], with typical correlation length  $\Lambda$ =30 nm and rootmean-square amplitude  $\Delta$ =1.3 nm, which is the level that is achieved with current lithography systems. The quoted in the literature values of LER are equal to  $3\Delta$ . The procedure used for simulating PGG involves the random generation of poly-grains for the whole gate region [3]: a large atomic force microscope image of polycrystalline silicon grains illustrated at the top of Fig. 3 has been used as a template and the image is scaled according to the average grain diameter (65 nm in the following simulations). Then the simulator imports a random section of the grain template image that corresponds to the gate dimension of the simulated device, and along grain boundaries, the applied gate potential in the polysilicon is modified in a way that the Fermi level remains pinned at a certain position in the silicon bandgap. In the worst case scenario the Fermi level is pinned in the middle of the silicon gap. The impact of polysilicon grain boundary variation on device characteristics is simulated through the pinning of the potential in the polysilicon gate along the grain boundaries. The individual impact of RDD, LER and PSG on the potential distribution in a typical 35 nm bulk MOSFET is illustrated in Figs. 7, 8 and 9 respectively.

The validation of our simulation technology is done in comparison with measured statistical variability data in 45 nm low power CMOS transistors [12]. The simulator was adjusted to match accurately the carefully calibrated TCAD device simulation results of devices without variability by adjusting the effective mass parameters involved in DG formalism, and the mobility model parameters.

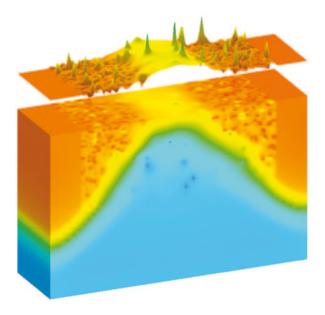

**Fig. 7** Potential distribution in a 35 nm MOSFET subject to RDD

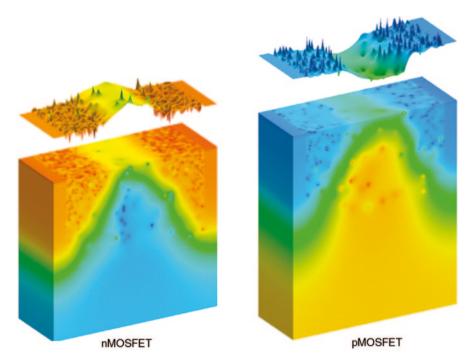

The potential distributions in the n- and p-channel transistors in Fig. 7, at gate voltage equal to the threshold voltage and low drain voltage of 50 mV, is illustrated in Fig. 10. In the n-channel transistor RDD, LER and PSG are considered simultaneously while in the p-channel transistor only RDD and LER are considered. The electron concentration at the interface of the two transistors is mapped on top of

**Fig. 8** Potential distribution in a 35 nm MOSFET subject to LER

Fig. 10 Top: electron (left) and hole (right) concentration distribution at the interface; Bottom: potential distribution

|              | n-channel MOSFET            |                            | p-channel MOSFET            |                            |  |

|--------------|-----------------------------|----------------------------|-----------------------------|----------------------------|--|

|              | $\sigma V_T(\text{mV})$     | $\sigma V_T(\text{mV})$    | $\sigma V_T(\text{mV})$     | $\sigma V_T(\text{mV})$    |  |

|              | $(V_{DS} = 0.05 \text{ V})$ | $(V_{DS} = 1.1 \text{ V})$ | $(V_{DS} = 0.05 \text{ V})$ | $(V_{DS} = 1.1 \text{ V})$ |  |

| RDD          | 50                          | 52                         | 51                          | 54                         |  |

| LER          | 20                          | 33                         | 13                          | 22                         |  |

| PSG          | 30                          | 26                         | _                           | _                          |  |

| Combined     | 62                          | 69                         | 53                          | 59                         |  |

| Experimental | 62                          | 67                         | 54                          | 57                         |  |

**Table 1**  $\sigma V_{\tau}$  introduced by individual and combined sources of statistical variability

the potential distributions. For example acceptors in the channel of the n-channel transistor create sharp localized potential barrier for the electrons near the interface but act as potential wells for the holes in the substrate. In the same time the donors in the source/drain regions create sharp potential well for electrons.

The simulation results for the standard deviation of the threshold voltage  $\sigma V_T$  introduced by individual and combined sources of statistical variability are compared with the measured data in Table 1. In the n-channel MOSFET case the accurate reproduction of the experimental measurements necessitates the assumption that, in addition to RDD and LER, the PSG related variability has to be taken into account. Good agreement has been obtained assuming that the Fermi level at the n-type poly-Si gate grain boundaries is pinned in the upper half of the bandgap at approximately 0.35 eV below the conduction band of silicon.

However, in the p-channel MOSFET case the combined effect of just the RDD and LER is sufficient to reproduce accurately the experimental measurements. The reason for this is the presence of acceptor type interface states in the upper half of the bandgap which pin the Fermi level in the case of n-type poly-Si, and the absence of corresponding donor type interface states in the lower part of the bandgap which leaves the Fermi level unpinned in the case of p-type poly-Si [13].

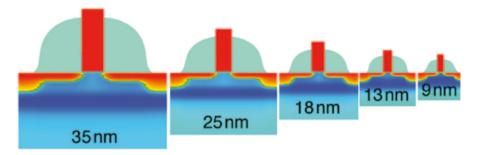

In order to foresee the expected magnitude of statistical variability in the future we have studied the individual impact of RDD, LER and PSG on MOSFETs with gate lengths 35, 25, 18, 13 and 9 nm physical gate length. We also compare the results with the statistical variability introduced in the same devices when RDD, LER and PSG are introduced in the same devices simultaneously. The scaling of the simulated devices is based on a 35 nm MOSFET published by Toshiba [14] against which our simulations were carefully calibrated. The scaling closely follows the prescriptions of the ITRS in terms of equivalent oxide thickness, junction depth, doping and supply voltage. The intention was also to preserve the main features of the reference 35 nm MOSFET and, in particular, to keep the channel doping concentration at the interface as low as possible. Figure 11 shows the structure of the scaled devices. More details about the scaling approach and the characteristics of the scaled devices may be found in [11].

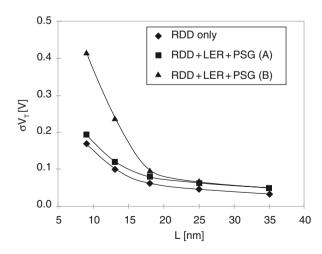

Figure 12 compares the channel length dependence of  $\sigma VT$  introduced by random dopants, line edge roughness and poly-Si grain boundaries with Fermi level

**Fig. 11** Examples of realistic conventional MOSFETs scaled from a template 35 nm device according to the ITRS requirements for the 90, 65, 45, 32 and 22 nm technologies, obtained from process simulation with Taurus Process

pinning. The average size of the polysilicon grains was kept at 40 nm for all channel lengths. Two scenarios for the magnitude of LER were considered in the simulations. In the first scenario the LER values decrease with the reduction of the channel length following the prescriptions of the ITRS 2003 of 1.2, 1.0, 0.75, and 0.5 nm for the 35-, 25-, 18-, and 13-nm channel length transistors, respectively. In this case the dominant source of variability at all channel lengths are the random discrete dopants. The variability introduced by the polysilicon granularity is similar to that introduced by random discrete dopants for the 35 nm and 25 nm MOSFETs, but at shorter channel lengths the random dopants take over. The combined effect of the three sources of variability is also shown in the same figure. In the second scenario LER remains constant and equal to its current value of approximately 4 nm ( $\Delta$ =1.33 nm). The results for the 35 nm and the 25 nm MOSFETs are very similar to the results with scaled LER but below 25 nm channel length LER rapidly becomes the dominant source of variability.

Fig. 12 Channel length dependence of  $\sigma V_T$  introduced by random dopants, line edge roughness and poly-Si granularity: (A) LER scales according ITRS; (B) LER=4 nm

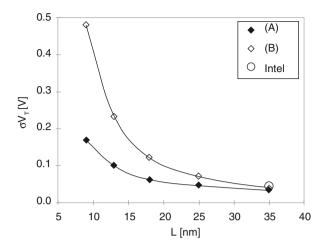

Fig. 13 Channel length dependence of  $\sigma V_T$  introduced by random dopants, line edge roughness and poly-Si granularity: (A)  $t_{\alpha x}$  scales according ITRS; (B)  $t_{\alpha x}$ =1 nm

Figure 12 is analogous to Fig. 13 exploring the scenario of the oxide thickness, which is difficult to scale further. The LER is scaled according to the ITRS requirements listed above. Even with the introduction of high-k gate stack it is likely to remain stagnated at 1 nm. This will lead to an explosion in the threshold voltage variability for bulk MOSFETs with physical channel length below 25 nm.

#### 4 Statistical Compact Model Strategy

It is very important to be able to capture the simulated or measured statistical variability in statistical compact models since this is the only way to communicate this information to designers [15]. Previous research on statistical compact model identification was focused mainly on variability associated with traditional process variations resulting from poor control of critical dimensions, layer thicknesses and doping clearly related to specific compact model parameters [16].

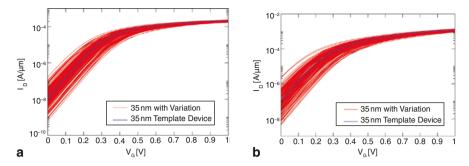

Unfortunately, the current industrial strength compact models do not have natural parameters designed to incorporate seamlessly the truly statistical variability associated with RDD, LER, PGG and other relevant variability sources. Despite some attempts to identify and extract statistical compact model parameters suitable for capturing statistical variability introduced by discreteness of charge and matter this remains an area of active research [16, 17]. Figure 14 shows the spread in ID–VG characteristics obtained from 'atomistic' simulator due to the combined effect of RDD, LER and PGG.

We use the standard BSIM4 compact model to capture the information for statistical variability obtained from full 3D physical variability simulation. The statistical extraction of compact model parameters is done in two stages [17].

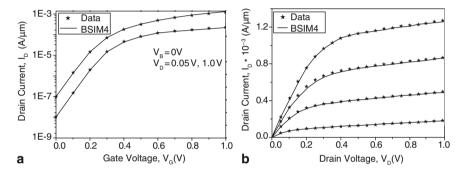

In the first stage, one complete set of BSIM4 parameters is extracted from the I–V characteristics of 'uniform' (continuously doped, no RDD, LER and PGG) set of devices with different channel lengths and widths and process flow identical to the one of the 35 nm testbed transistor (Fig. 15). Target current voltage char-

Fig. 14 Variability in the current voltage characteristics of a statistical sample of 200 microscopically different 25 nm square (W=L) n-channel MOSFETs at a  $V_D$ =50 mV and b  $V_D$ =1 V

Fig. 15 Comparison of a  $I_D$ – $V_G$  characteristics, b  $I_D$ – $V_D$  for characteristics for 'uniform' devices obtained from physical simulations and BSIM

acteristics are simulated over the complete device operating range and parameter extraction strategy combining group extraction and local optimization is employed. Figure 16 compares the corresponding BSIM4 generated I–V characteristics of the 35 nm transistor with the original device characteristics obtained from our 'atomistic' simulator. The RMS error for this extraction is 2.8%.

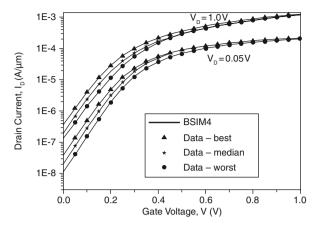

At the second stage, we re-extracted a small carefully chosen subset of the BSIM4 model parameters from the physically simulated characteristics of each microscopically different device in the statistical ensemble keeping the bulk of the BSIM parameters unchanged. The transfer (ID–VG) characteristics at low and high drain bias are used as extraction target at this stage. The seven re-extracted model parameters are  $L_{pe0}$ ,  $R_{dswmin}$ ,  $N_{factor}$ ,  $V_{off}$ ,  $A_1$ ,  $A_2$  and  $D_{sub}$ . Figure 16 compares the BSIM4 results for the worst, the best and the typical de-

Figure 16 compares the BSIM4 results for the worst, the best and the typical devices with the physically simulated device characteristics. The good match between the BSIM results and the physically device characteristics validates the choice of seven parameters which guaranty high accuracy of the compact model over the whole statistical range of physically simulated device characteristics. Figure 17 illustrates the distribution in the error of the 200 statistically different BSIM4 cards depending on the density of the data points in the ID–VG characteristics used as

Fig. 16 Comparison of physical and simulation results obtained after second stage statistical extraction for the devices with best, worst and median extraction error

targets in the statistical compact model extraction. Relatively few simulation data points are needed to extract high accuracy statistical compact model parameters.

Above statistical compact model extraction and 3D physical device simulation are based on minimum size square device (W=L), which has the maximum magnitude of statistical variation. However, in real circuits, most of devices have multiwidth/length ratio value. In order to reproduce the right statistical behavior of such devices in statistical circuit simulation, wider device are constructed by connecting in parallel minimum size devices randomly selected from the statistic compact model library.

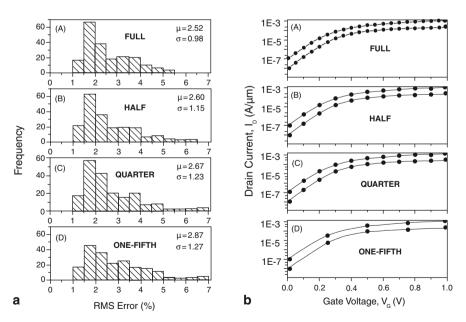

Fig. 17 Distribution of the statistical error as a function of a different number of data points on the target  $I_D - V_G$  characteristics used in the statistical compact model extraction

#### 5 Impact of Statistical Variability on SRAM

One area where the digital and the analogue design expertise overlap is in the design of SRAM and particularly SRAM cells which are extremely sensitive to statistical variability. The statistical circuit simulation methodology described in the previous section, which can transfer all the fluctuation information obtained from 3D statistical device simulations into circuit simulation, is employed to investigate the impact of RDF on 6T and 8T SRAM stability for the next three generations of bulk CMOS technology. In the following discussions, we use 25, 18 and 13 nm channel length transistors from Sect. 3.

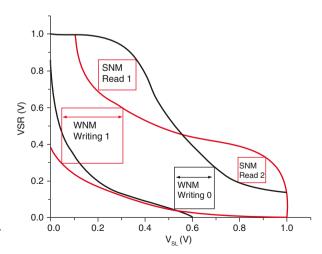

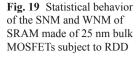

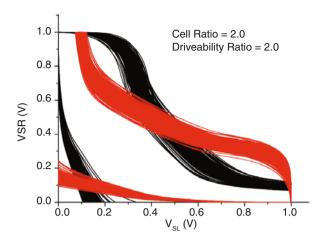

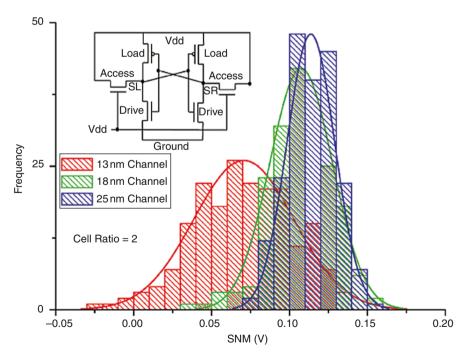

Currently, 6T SRAM is the dominant SRAM cell architecture in SoC and microprocessors. However, the disturbance of bit lines on the data retention element during read access makes the 6T cell structure vulnerable to statistical variability, which in turn will have a huge impact on 6T SRAM's scalability. The functionality of SRAM is determined by both static noise margin (SNM) defined as the minimum dc voltage necessary to flip the state of the cell and the write noise margin (WNM) defined as the DC noise voltage needed to fail to flip a cell during a write period. The meaning of SNM and WNM is defined in Fig. 18. Figure 19 illustrates the statistical nature of SNM and WNM in the presence of statistical transistor variability.

The magnitude of WNM in SRAM is mainly determined by the load and access transistors illustrated in the 6T SRAM schematics inset in Fig. 20. Since they are the smallest transistors in an SRAM cell, the WNM variation will be larger than the SNM variation. However, the mean value of WNM is much larger than its SNM counterpart. Previous studies [18] suggested that under normal circumstances the limiting factor for the operation of bulk 6T SRAM cells is SNM.

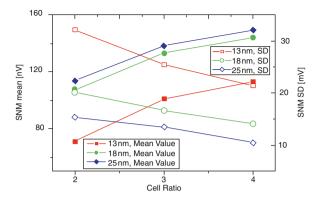

The statistical circuit simulation results for the distribution of SNM for 6T SRAM with the cell ratio of 2 is shown in Fig. 20, while the schematic of a 6T

Fig. 18 Static voltage transfer characteristics and definition of SNM and WNM

SRAM cell with the bias configuration at the initiation of read operation is illustrated in the inset. The cell ratio is defined as the ratio of the driver transistor to access resistor channel widths. For the 13 nm generation, around 2% of SRAM cells with cell ratio of 2 are not readable even under ideal conditions since their SNM values are negative. The standard deviation  $\sigma$  of SNM, normalized by the

Fig. 20 Distribution of 6T SRAM SNM over an ensemble of 200 SRAM cells for 25, 18 and 13 nm generations

average value  $\mu$  of the SNM increases from 13% for the 25 nm generation, to 19% for the 18 nm generation, and reaches 45% for the 13 nm generation. As a guideline,  $\mu$  –  $6\sigma$  is required to exceed approximately 4% of the supply voltage to achieve 90% yield for 1 Mbit SRAM's. Although the 25 nm generation is three times better with respect to SNM fluctuation performance compared to the 13 nm generation at cell ratio of 2, it still cannot meet the " $\mu$  –  $6\sigma$ " test on yield control.

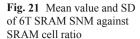

Increasing the cell ratio is the most straightforward way to improve SNM performance of a SRAM cell [19]. The mean value ( $\mu$ ) and the standard deviation ( $\sigma$ ) of SNM at different SRAM cell ratios are shown in Fig. 21, which clearly illustrates the benefits of larger cell ratio. For the 25 nm transistors, the increase of the cell ratio from 2 to 4 results in nearly two times NSD of SNM improvement, and the " $\mu$  –  $6\sigma$ " criterion is met at a cell ratio of 3. Although the 18 nm and 13 nm generations follow a similar trend, a cell ratio of 4 is required for 18 nm technology in order to achieve reasonable yield. For the 13 nm generation, a cell ratio of 4 can only achieve the level of performance of the 18 nm generation at a cell ratio of 2. At the same time, the increase in the cell ratio tends to degrade the WNM. Therefore, the approach of increasing the cell ratio becomes less attractive for extremely scaled devices even from the prospect of the yield.

#### 6 Conclusions

The statistical variability introduced by discreteness of charge and matter has become one of the major concerns for the semiconductor industry. More and more the strategic technology decisions that the industry will be making in the future will be motivated by the desire to reduce statistical variability. The useful life of bulk MOSFETs, from statistical variability point of view, can be extended below the 20 nm technology mark only if the line edge roughness and the equivalent oxide thickness could be successfully scaled to the required values. SRAM which uses

minimum channel width transistors is the most sensitive part of the integrated systems in respect of statistical variability and needs special care and creative design solution in order to take full advantage from scaling in present and future technology generations.

#### References

- G.E. Moore, Progress in Digital Electronics, in Technical Digest of the Int'l Electron Devices Meeting. Washington DC, Dec 1975, p. 13

- K. Bernstein, D.J. Frank, A.E. Gattiker, W. Haensch, B.L. Ji, S.R. Nassif, E.J. Nowak, D.J. Pearson, N.J. Rohrer, IBM J. Res. Dev. 50, 433 (2006)

- 3. A.R. Brown, G. Roy, A. Asenov, Poly-Si gate related variability in decananometre MOSFETs with conventional architecture. IEEE Trans. Electron. Dev. **54**, 3056 (2007)

- 4. B.-J. Cheng, S. Roy, A. Asenov, The impact of random dopant effects on SRAM cells, in *Proc. 30th European Solid-State Circuits Conference (ESSCIRC)*, Leuven, 2004, p. 219

- 5. A. Agarwal, K. Chopra, V. Zolotov, D. Blaauw, Circuit optimization using statistical static timing analysis, in *Proc. 42nd Design Automation Conference*, Anaheim, 2005, p. 321

- A. Asenov, Random dopant induced threshold voltage lowering and fluctuations in sub 0.1 micron MOSFETs: A 3D 'atomistic' simulation study. IEEE Trans. Electron. Dev. 45, 2505 (1998)

- A. Asenov, S. Kaya, A.R. Brown, Intrinsic parameter fluctuations in decananometre MOS-FETs introduced by gate line edge roughness. IEEE Trans. Electron. Dev. 50, 1254 (2003)

- 8. J.R. Watling, A.R. Brown, G. Ferrari, J.R. Babiker, G. Bersuker, P. Zeitzoff, A. Asenov, Impact of High-k on transport and variability in nano-CMOS devices. J. Comput. Theo. Nanosci. 5(6), 1072 (2008)

- 9. A. Asenov, S. Kaya, J.H. Davies, Intrinsic threshold voltage fluctuations in decanano MOS-FETs due to local oxide thickness variations. IEEE Trans. Electron. Dev. **49**, 112 (2002)

- A.R. Brown, J.R. Watling, A. Asenov, A 3-D atomistic study of archetypal double gate MOS-FET structures. J. Comput. Electron. 1, 165 (2002)

- 11. G. Roy, A.R. Brown, F. Adamu-Lema, S. Roy, A. Asenov, Simulation study of individual and combined sources of intrinsic parameter fluctuations in Conventional Nano-MOSFETs. IEEE Trans. Electron. Dev. **52**, 3063–3070 (2006)

- A. Cathignol, B. Cheng, D. Chanemougame, A.R. Brown, K. Rochereau, G. Ghibaudo, A. Asenov, Quantitative evaluation of statistical variability sources in a 45 nm technological node LP N-MOSFET. IEEE Electron. Dev. Lett. 29, 609 (2008)

- 13. A. Asenov, A. Cathignol, B. Cheng, K.P. McKenna, A.R. Brown, A.L. Shluger, D. Chanemougame, K. Rochereau, G. Ghibaudo, Origin of the asymmetry in the magnitude of the statistical variability of n- and p-Channel poly-Si gate bulk MOSFETs. IEEE Electron. Dev. Lett. 29, 913–915 (2008)

- S. Inaba, K. Okano, S. Matsuda, M. Fujiwara, A. Hokazono, K. Adachi, K. Ohuchi, H. Suto, H. Fukui, T. Shimizu, S. Mori, H. Oguma, A. Murakoshi, T. Itani, T. Iinuma, T. Kudo, H. Shibata, S. Taniguchi, M. Takayanagi, A. Azuma, H. Oyamatsu, K. Suguro, Y. Katsumata, Y. Toyoshima, H. Ishiuchi, High performance 35 nm gate length CMOS with NO oxynitride gate dielectric and Ni salicide. IEEE Trans. Electron. Dev. 49, 2263 (2002)

- 15. M. Denais, V. Huard, C. Parthasarathy, G. Ribes, F. Perrier, N. Revil, A. Bravaix, Interface trap generation and hole trapping under NBTI and PBTI in advanced CMOS technology with a 2-nm gate oxide. IEEE Trans. Dev. Mater. Reliab. 4, 715 (2004)

- C.C. McAndrew, Efficient statistical modeling for circuit simulation, in *Design of Systems on a Chip: Devices and Components*, ed. by R. Reis, J. Jess (Kluwer, Dordrecht, 2004), p. 97. ISBN 978-1-4020-7929-0

- 17. K. Takeuchi, M. Hane, Statistical compact model parameter extraction by direct fitting to. IEEE Trans. Electron. Dev. 55, 1487 (2008)

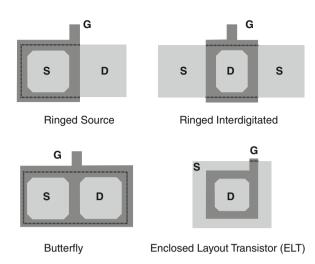

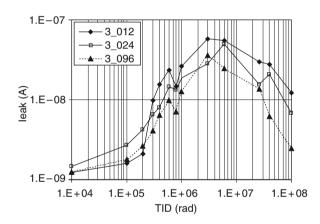

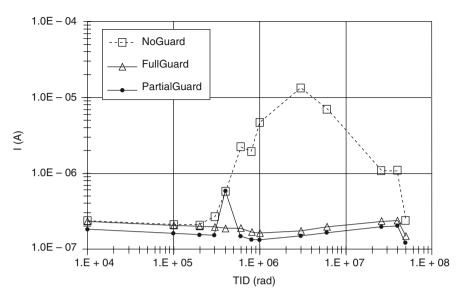

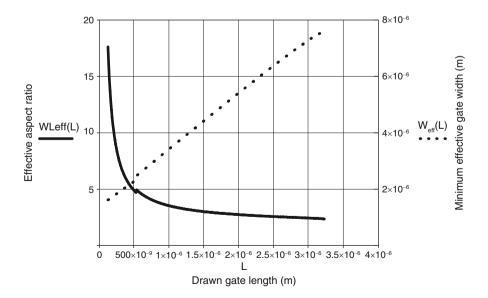

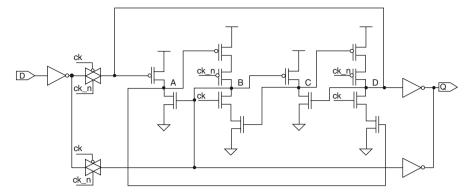

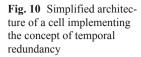

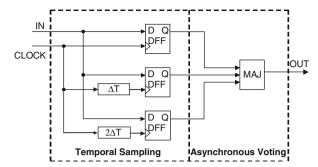

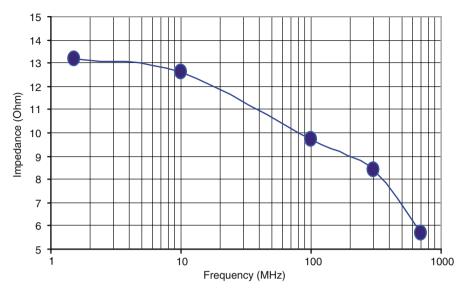

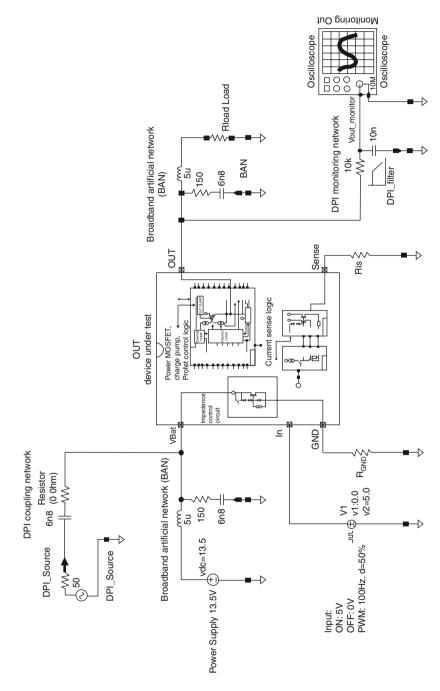

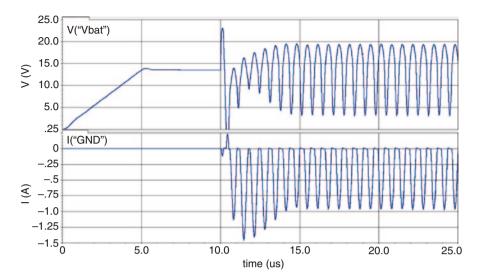

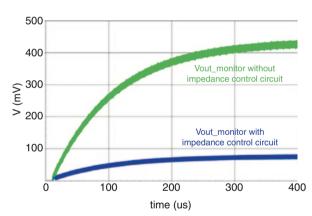

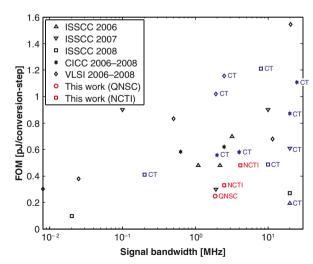

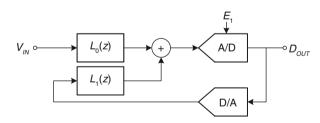

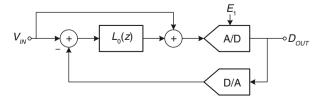

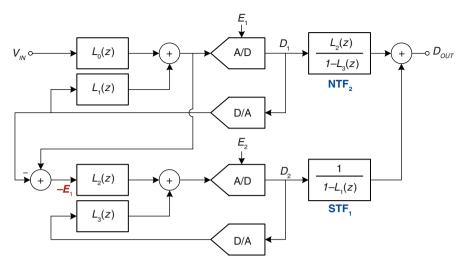

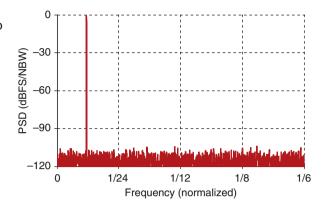

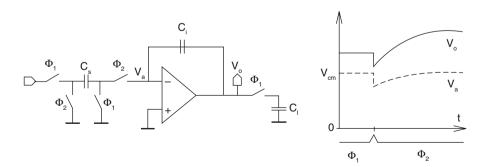

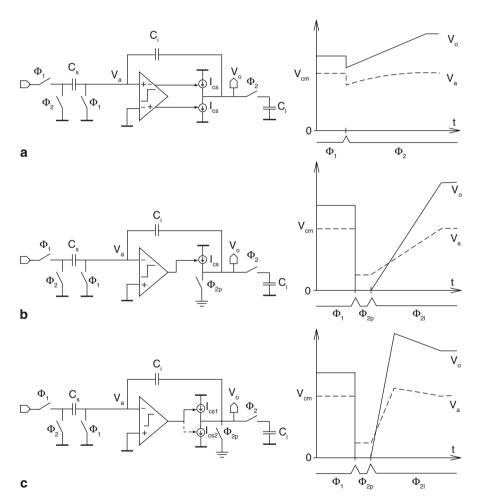

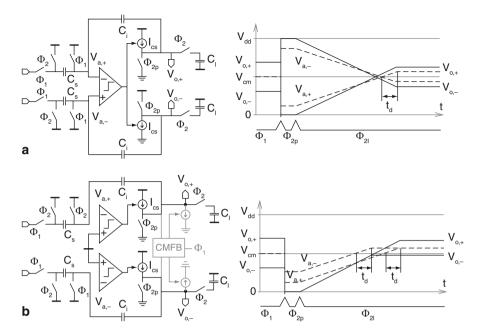

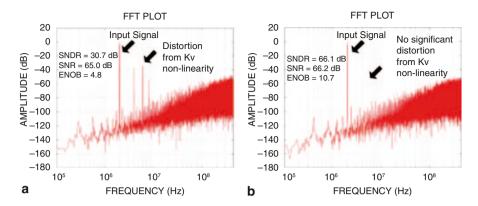

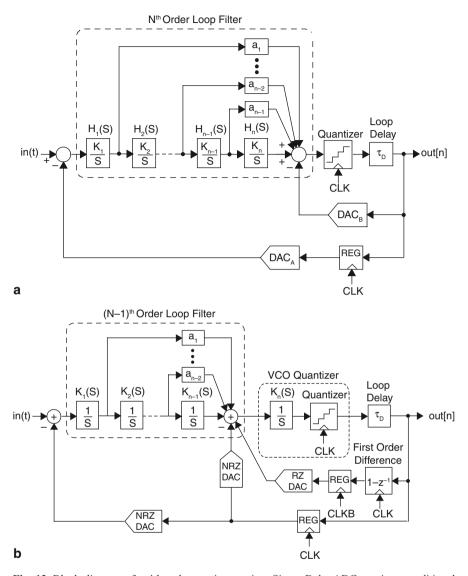

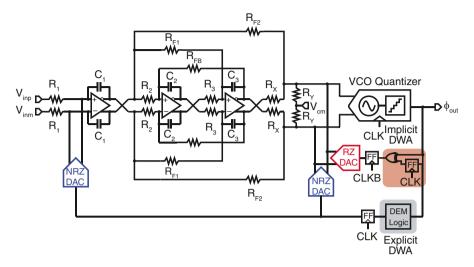

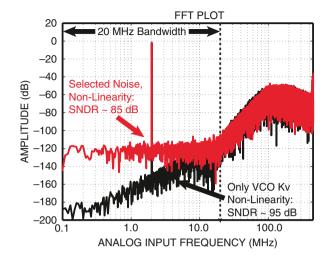

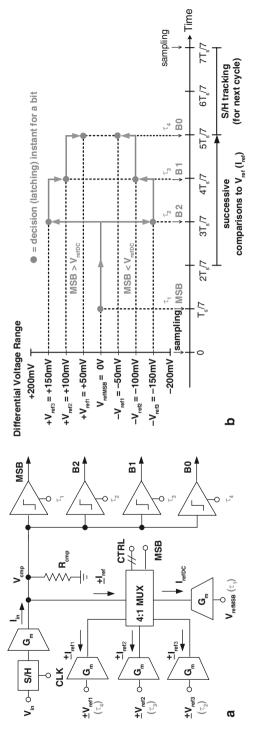

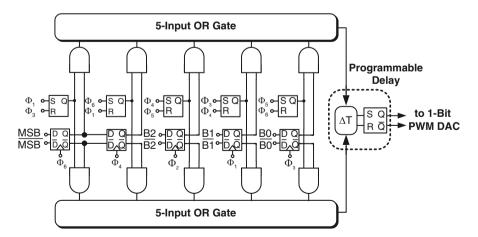

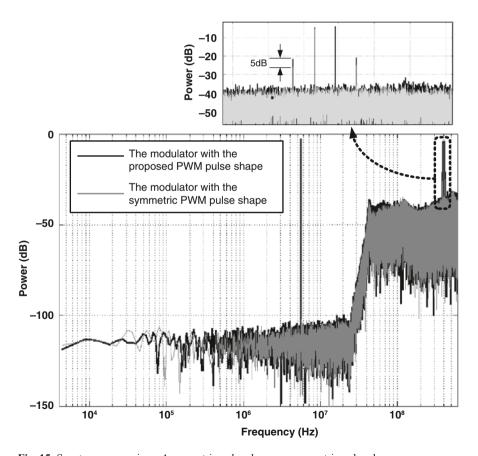

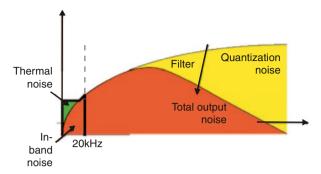

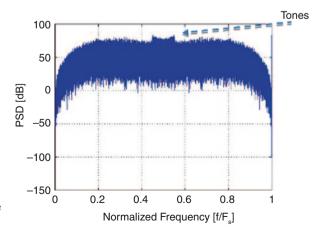

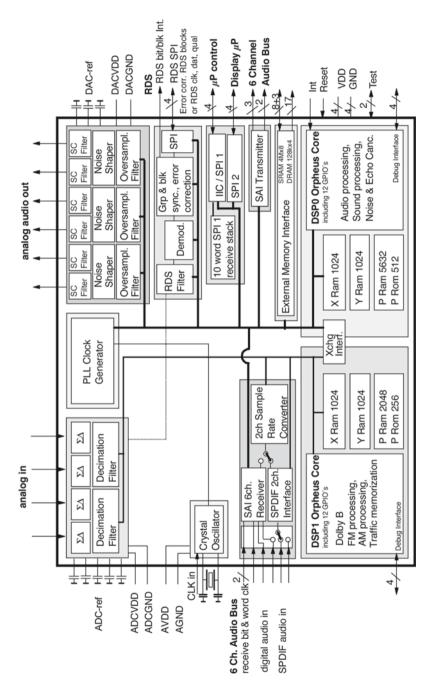

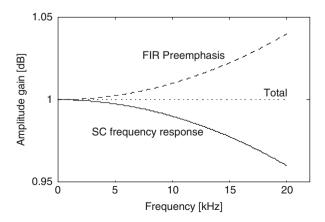

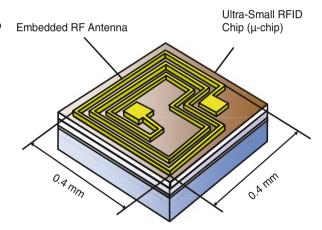

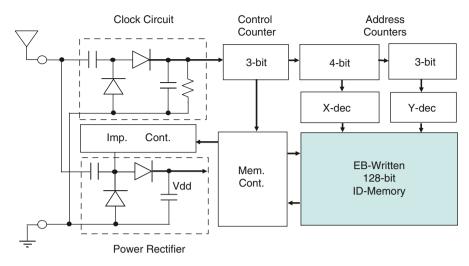

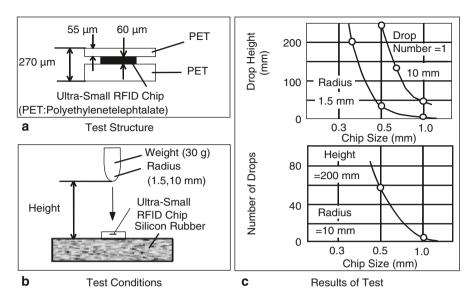

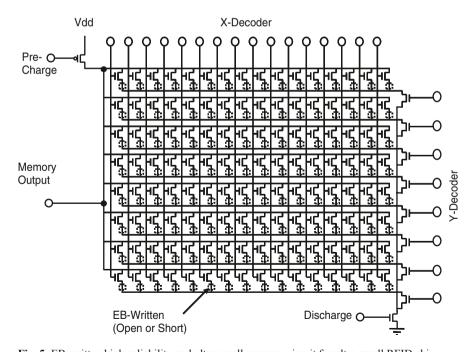

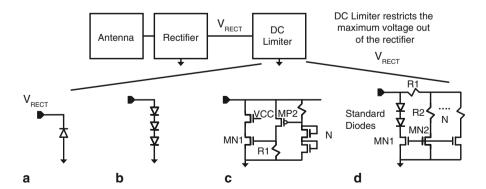

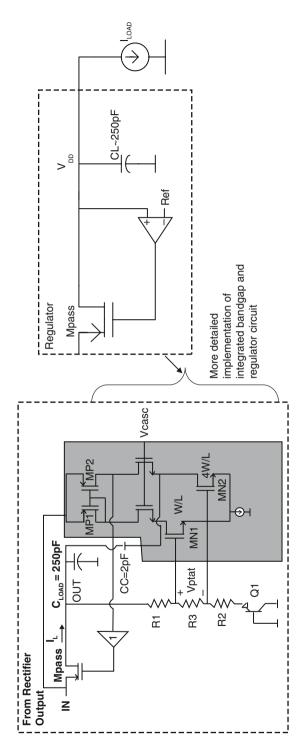

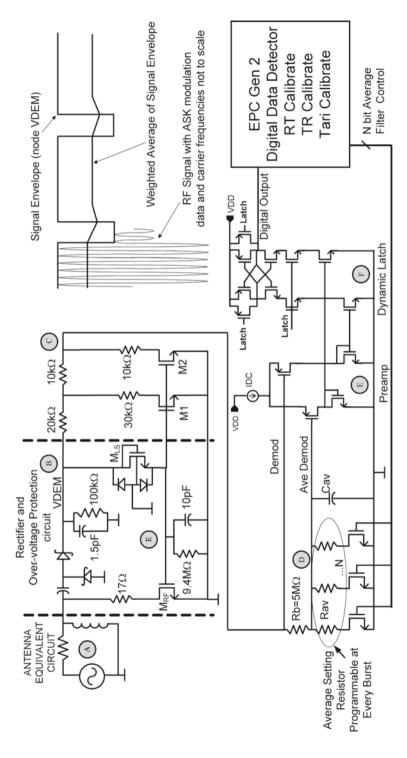

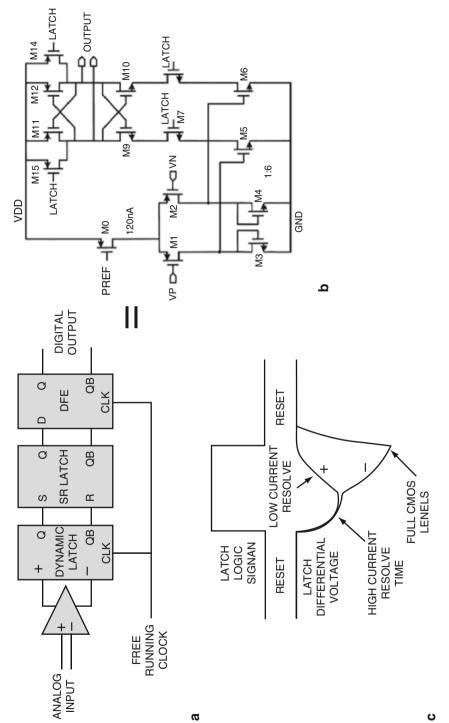

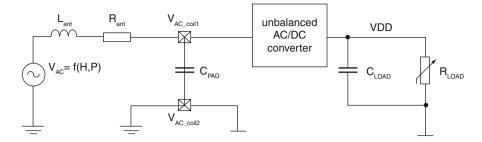

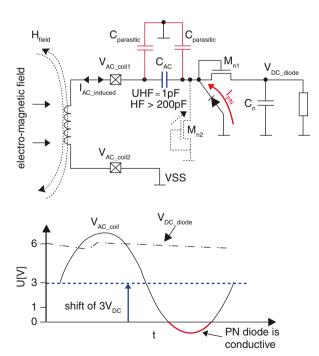

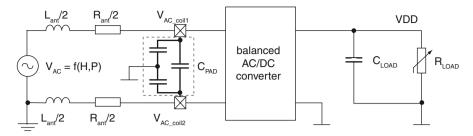

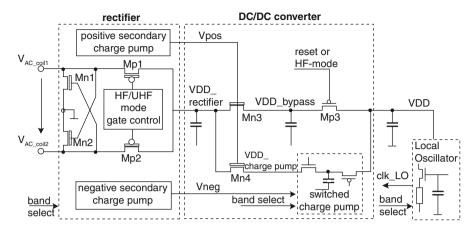

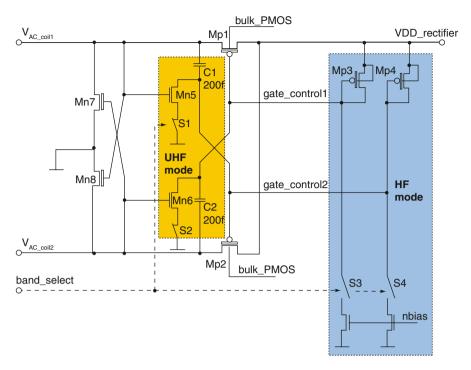

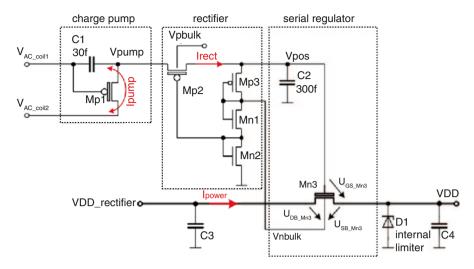

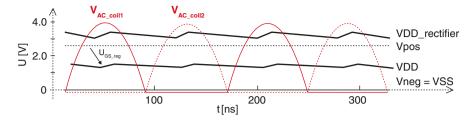

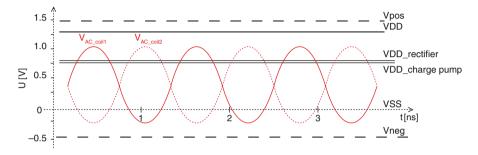

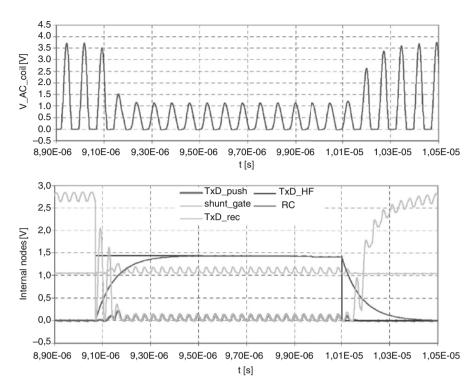

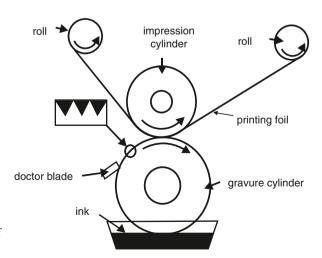

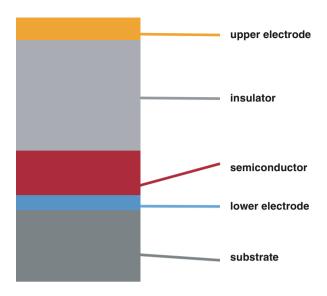

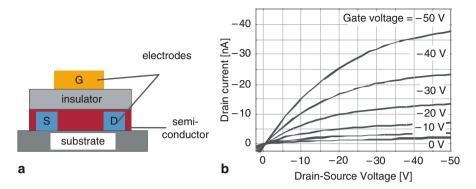

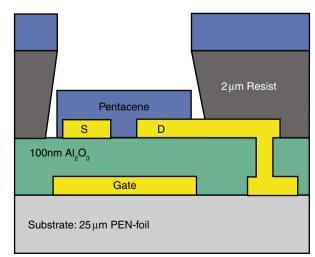

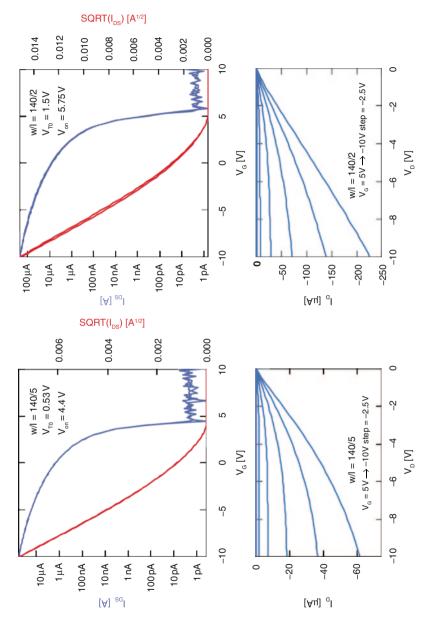

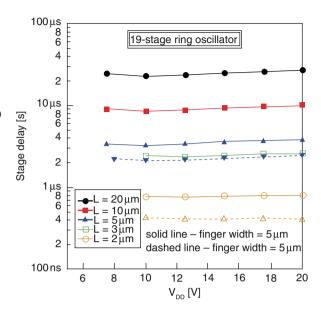

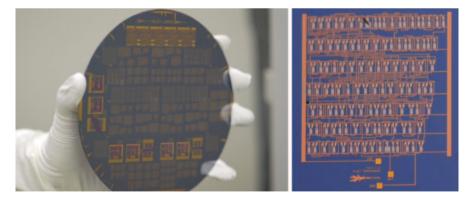

- B. Cheng, S. Roy, G. Roy, F. Adamu-Lema, A. Asenov, Impact of intrinsic parameter fluctuations in decanano MOSFETs on yield and functionality of SRAM cells. Solid-State Electron. 49, 740 (2005)